2004. augusztus 30. 20:11, Hétfő

Ahogy a tranzisztorok egyre kisebbé válnak, a teljesítmény és a hőtermelés egyre inkább növekszik. Ennek eredményeként az új technikák és struktúrák bevezetésekor elkerülhetetlen csökkenteni ezen folyamatok káros hatásait.

"Az Intel új anyagokkal, új technológiákkal és új eszközstruktúrákkal továbbra is megpróbál eleget tenni a növekvő skálázhatósági kihívásoknak" - mondta Sunlin Chou, az Intel alelnöke és gyártástechnológiáért felelős ügyvezető igazgatója. "Az Intel 65 nm-es gyártási technológiája iparágvezető sűrűséggel, teljesítménnyel és energiatakarékos képességekkel rendelkezik: mindezek a jövő chipjeiben további potenciált és nagyobb teljesítményt vetít elő."

Moore törvénynek megfelelően az egy chipben lévő tranzisztorok száma nagyjából minden második évben megduplázódik, amely új képességeket, megnövekedett teljesítményt és csökkentett tranzisztoronkénti költséget jelent. Az Intel az integrált energiatakarékos képességekkel próbál megfelelni a bevezetőben említett kihívásoknak. Ezen tulajdonságok kritikusak az energiagazdaságos számítástechnikához és a jövő kommunikációs termékeihez.

A vállalat feszített szilícium technológiáját - melyet először a 90 nm-es eljárás során használatak - a 65 nm-es technológiában is továbbfejlesztette. A feszített szilícium második generációja 10-15 százalékkal növeli a tranzisztorok teljesítményét, a szivárgás növekedése nélkül. Adott teljesítmény mellett a tranzisztorokban létrejövő szivárgás a 90 nm-es tranzisztorokhoz képest negyedére csökkent. Ennek eredményeként az Intel 65 nm-es eljárásához használt tranzisztorok megnövekedett teljesítményt nyújtanak, jelentős szivárgásemelkedés nélkül (a nagyobb szivárgási áram nagyobb hőtermelést eredményez).

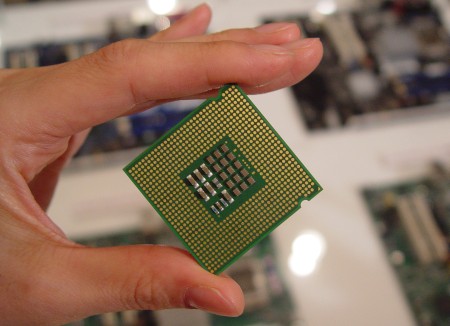

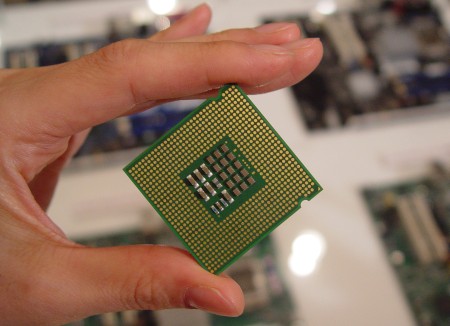

2003 novemberében a cég bejelentette, hogy 65 nanométeres gyártási technológiával készítette el 4 megabites SRAM-jait. Azóta a vállalat több teljes funkcionalitású 70 megabites SRAM-ot épített ezzel az eljárással egy nagyon apró, mindössze 110 mm

2-es területre. A kis SRAM cellák lehetővé teszik a nagyobb gyorsítótárak processzorokhoz való integrációját, amely által nő a teljesítmény. Minden SRAM memóriacella hat tranzisztorból áll egy 0,57 négyzetmikrométeres területen. Néhány 10 millió tranzisztorok elfér egy csupán egy négyzetmilliméteres helyre, amely nagyjából egy golyóstoll hegyének nagyságával egyezik meg.

A társaság 65 nanométeres tranzisztorainak kapuhosszúsága (gate) csökkentett, és a kapu-oxid (gate oxide) vastagsága 1,2 nanométer, ami által nő a teljesítmény, illetve csökken a kapu kapacitása. A csökkentett kapacitás végső soron csökkenti a chip aktív fogyasztását. Az új technológia segítségével nyolcrétegű alkatrészek állíthatók elő réz alapú átkötésekkel, illetve alacsony k-együtthatójú dielektrikummal, így a chipen belül nő a jelek gyorsasága, illetve csökken az energiaigény.

A cég emellett "alvó tranzisztorokat" is beépített a 65 nm-es SRAM-okba. Az alvó tranzisztorok lezárják a SRAM nagyobb építőkockáihoz irányuló áramot, amikor ezek nincsenek használva; így jelentős chip energiaigény-igény forrást küszöböl ki. Ezen tulajdonság különösen előnyös az akkumulátoros eszközök, különösen a laptopok számára. "Az Intel hatékony megoldást próbál találni a félvezetőipar kihívásainak megválaszolására, többek között az energia- és hőpazarlás kérdéseiben" - mondta Chou. "A különböző rendszer-, chip- és technológiai megoldások kifejlesztésével, és a 65 nm-es technológiához hasonló innovációk által teljeskörű megközelítést alakítottunk ki ezen kihívások terén."

Az Intel 65 nm-es félvezető eszközeit a vállalat hillsborói fejlesztési üzemében gyártják, ahol a gyártástechnológiát kifejlesztették. A társaság új technológiájáról további részletek kerülnek nyilvánosságra a San Franciscó-i IEEE International Electron Devices Meeting - találkozó alkalmával, december 12. és 15. között.

Informatika és tudomány

Informatika és tudomány

Informatika és tudomány

Informatika és tudomány